Infineon C7 GOLD Type N-Channel MOSFET & Diode, 83 A, 650 V Enhancement, 10-Pin HDSOP IPDD60R080G7XTMA1

- RS-stocknr.:

- 220-7418

- Fabrikantnummer:

- IPDD60R080G7XTMA1

- Fabrikant:

- Infineon

Bulkkorting beschikbaar

Subtotaal (1 verpakking van 2 eenheden)*

€ 5,65

(excl. BTW)

€ 6,836

(incl. BTW)

GRATIS bezorging voor bestellingen van meer dan € 75,00

Op voorraad

- Plus verzending 1.700 stuk(s) vanaf 23 maart 2026

Heeft u meer nodig? Klik op 'Controleer leverdata' voor extra voorraad en levertijden.

Aantal stuks | Per stuk | Per verpakking* |

|---|---|---|

| 2 - 8 | € 2,825 | € 5,65 |

| 10 - 18 | € 2,75 | € 5,50 |

| 20 - 48 | € 2,675 | € 5,35 |

| 50 - 98 | € 2,61 | € 5,22 |

| 100 + | € 2,545 | € 5,09 |

*prijsindicatie

- RS-stocknr.:

- 220-7418

- Fabrikantnummer:

- IPDD60R080G7XTMA1

- Fabrikant:

- Infineon

Specificaties

Datasheets

Wetgeving en compliance

Productomschrijving

Zoek vergelijkbare producten door een of meer kenmerken te selecteren.

Alles selecteren | Attribuut | Waarde |

|---|---|---|

| Merk | Infineon | |

| Product Type | MOSFET & Diode | |

| Channel Type | Type N | |

| Maximum Continuous Drain Current Id | 83A | |

| Maximum Drain Source Voltage Vds | 650V | |

| Package Type | HDSOP | |

| Series | C7 GOLD | |

| Mount Type | Surface | |

| Pin Count | 10 | |

| Maximum Drain Source Resistance Rds | 80mΩ | |

| Channel Mode | Enhancement | |

| Forward Voltage Vf | 0.8V | |

| Maximum Gate Source Voltage Vgs | 20 V | |

| Typical Gate Charge Qg @ Vgs | 42nC | |

| Maximum Power Dissipation Pd | 174W | |

| Height | 21.11mm | |

| Length | 6.6mm | |

| Width | 2.35 mm | |

| Standards/Approvals | No | |

| Automotive Standard | No | |

| Alles selecteren | ||

|---|---|---|

Merk Infineon | ||

Product Type MOSFET & Diode | ||

Channel Type Type N | ||

Maximum Continuous Drain Current Id 83A | ||

Maximum Drain Source Voltage Vds 650V | ||

Package Type HDSOP | ||

Series C7 GOLD | ||

Mount Type Surface | ||

Pin Count 10 | ||

Maximum Drain Source Resistance Rds 80mΩ | ||

Channel Mode Enhancement | ||

Forward Voltage Vf 0.8V | ||

Maximum Gate Source Voltage Vgs 20 V | ||

Typical Gate Charge Qg @ Vgs 42nC | ||

Maximum Power Dissipation Pd 174W | ||

Height 21.11mm | ||

Length 6.6mm | ||

Width 2.35 mm | ||

Standards/Approvals No | ||

Automotive Standard No | ||

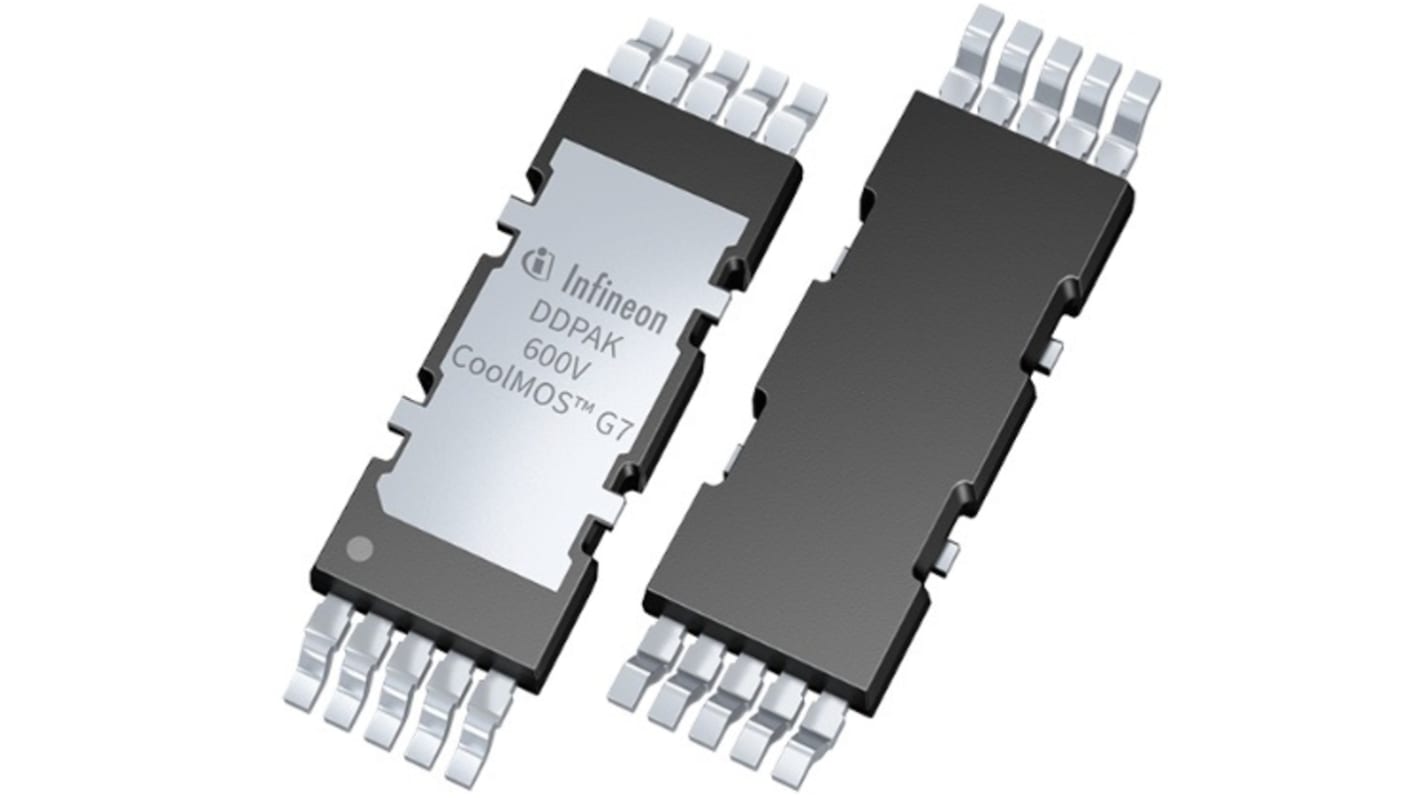

The Infineon technologies introduces Double DPAK (DDPAK), the first top-side cooled surface mount device (SMD) package addressing high power SMPS applications such as PC power, solar, server and telecom. The benefits of the already existing high voltage technology 600V Cool MOS G7 super junction (SJ) MOSFETis combined with the innovative concept of top-side cooling, providing a system solution for high current hard switching topologies such as PFC and a high-end efficiency solution for LLC topologies.

Gives best-in-class FOM RDS(on) x Eoss and RDS(on) x Qg

Innovative top-side cooling concept

Inbuilt 4th pin Kelvin source configuration and low parasitic source inductance

TCOB capability of >> 2.000 cycles, MSL1 compliant and total Pb-free

Enabling highest energy efficiency

Thermal decoupling of board and semiconductor allows to overcome thermal PCB limits

Reduced parasitic source inductance improves e efficiency and ease-of-use

Enables higher power density solutions

Exceeding the highest quality standards

Gerelateerde Links

- Infineon C7 GOLD Type N-Channel MOSFET & Diode 650 V Enhancement, 10-Pin HDSOP

- Infineon C7 GOLD Type N-Channel MOSFET & Diode 650 V Enhancement, 10-Pin HDSOP

- Infineon C7 GOLD Type N-Channel MOSFET & Diode 650 V Enhancement, 10-Pin HDSOP IPDD60R150G7XTMA1

- Infineon C7 GOLD Type N-Channel MOSFET 650 V Enhancement, 8-Pin HSOF

- Infineon C7 GOLD Type N-Channel MOSFET 650 V Enhancement, 8-Pin HSOF IPT60R150G7XTMA1

- Infineon CoolMOS C7 Type N-Channel MOSFET 650 V Enhancement, 5-Pin VSON

- Infineon CoolMOS C7 Type N-Channel MOSFET 650 V Enhancement, 5-Pin VSON IPL65R130C7AUMA1

- Infineon CoolMOS C7 Type N-Channel MOSFET 650 V Enhancement, 3-Pin TO-220