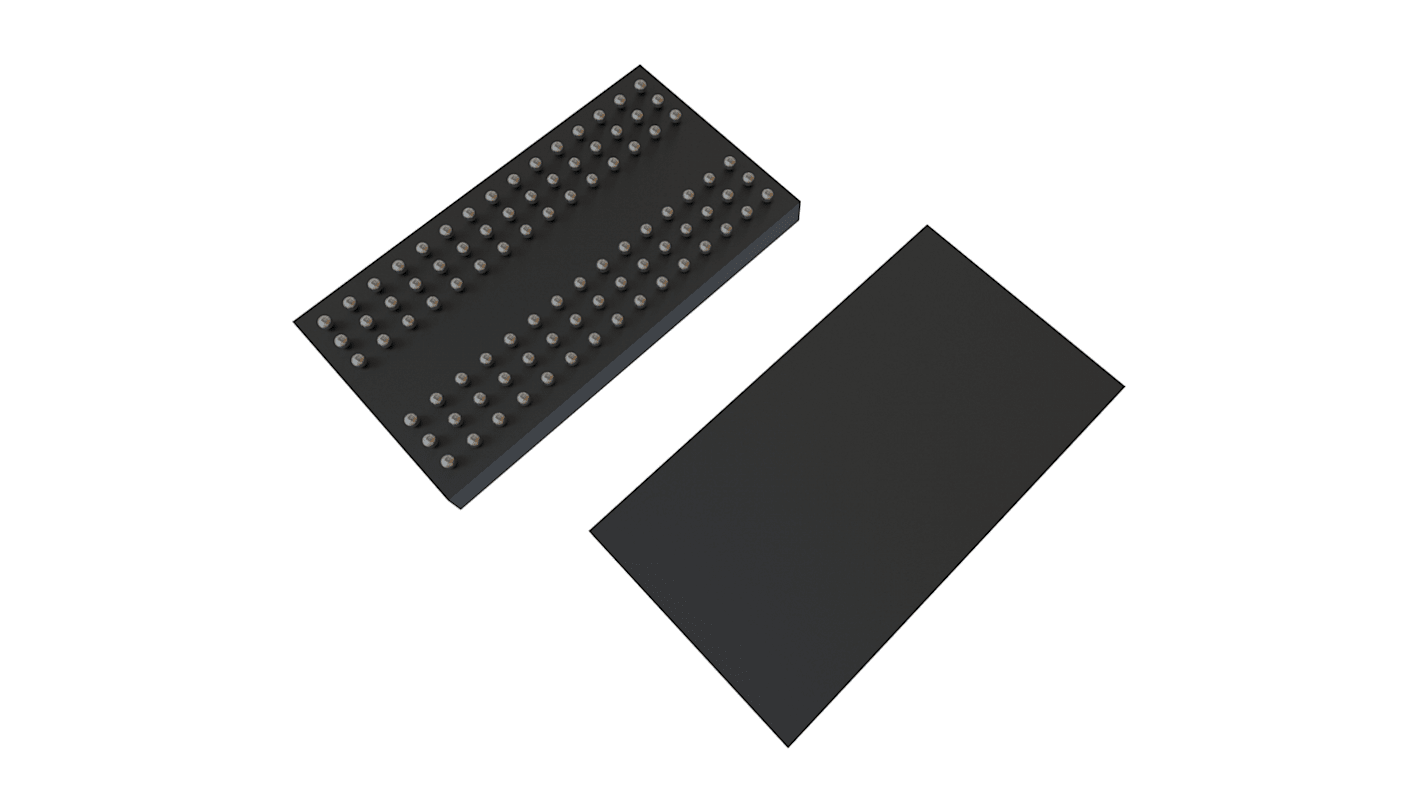

Winbond DDR2 SDRAM 128 MB Surface, 84-Pin 16 bit TFBGA

- RS-stocknr.:

- 188-2580

- Fabrikantnummer:

- W9712G6KB25I

- Fabrikant:

- Winbond

Subtotaal (1 tray van 209 eenheden)*

€ 370,557

(excl. BTW)

€ 448,305

(incl. BTW)

Informatie over voorraden is momenteel niet toegankelijk - Controleer het later nog eens opnieuw

Aantal stuks | Per stuk | Per tray* |

|---|---|---|

| 209 + | € 1,773 | € 370,56 |

*prijsindicatie

- RS-stocknr.:

- 188-2580

- Fabrikantnummer:

- W9712G6KB25I

- Fabrikant:

- Winbond

Specificaties

Datasheets

Wetgeving en compliance

Productomschrijving

Zoek vergelijkbare producten door een of meer kenmerken te selecteren.

Alles selecteren | Attribuut | Waarde |

|---|---|---|

| Merk | Winbond | |

| Memory Size | 128MB | |

| Product Type | DDR2 SDRAM | |

| Data Bus Width | 16bit | |

| Address Bus Width | 15bit | |

| Number of Bits per Word | 8 | |

| Maximum Random Access Time | 0.4ns | |

| Number of Words | 16M | |

| Mount Type | Surface | |

| Package Type | TFBGA | |

| Minimum Operating Temperature | -40°C | |

| Pin Count | 84 | |

| Maximum Operating Temperature | 95°C | |

| Standards/Approvals | RoHS | |

| Series | W9712G6KB | |

| Length | 12.6mm | |

| Height | 0.8mm | |

| Minimum Supply Voltage | 1.7V | |

| Supply Current | 135mA | |

| Automotive Standard | No | |

| Maximum Supply Voltage | 1.9V | |

| Alles selecteren | ||

|---|---|---|

Merk Winbond | ||

Memory Size 128MB | ||

Product Type DDR2 SDRAM | ||

Data Bus Width 16bit | ||

Address Bus Width 15bit | ||

Number of Bits per Word 8 | ||

Maximum Random Access Time 0.4ns | ||

Number of Words 16M | ||

Mount Type Surface | ||

Package Type TFBGA | ||

Minimum Operating Temperature -40°C | ||

Pin Count 84 | ||

Maximum Operating Temperature 95°C | ||

Standards/Approvals RoHS | ||

Series W9712G6KB | ||

Length 12.6mm | ||

Height 0.8mm | ||

Minimum Supply Voltage 1.7V | ||

Supply Current 135mA | ||

Automotive Standard No | ||

Maximum Supply Voltage 1.9V | ||

The W9712G6KB is a 128M bits DDR2 SDRAM and speed involving -25, 25I and -3.

Double Data Rate architecture: two data transfers per clock cycle

CAS Latency: 3, 4, 5 and 6

Burst Length: 4 and 8

Bi-directional, differential data strobes (DQS and /DQS ) are transmitted / received with data

Edge-aligned with Read data and center-aligned with Write data

DLL aligns DQ and DQS transitions with clock

Differential clock inputs (CLK and /CLK)

Data masks (DM) for write data

Commands entered on each positive CLK edge, data and data mask are referenced to both edges of /DQS

Posted /CAS programmable additive latency supported to make command and data bus efficiency

Read Latency = Additive Latency plus CAS Latency (RL = AL + CL)

Off-Chip-Driver impedance adjustment (OCD) and On-Die-Termination (ODT) for better signal quality

Auto-precharge operation for read and write bursts

Auto Refresh and Self Refresh modes

Precharged Power Down and Active Power Down

Write Data Mask

Write Latency = Read Latency - 1 (WL = RL - 1)

Interface: SSTL_18

Gerelateerde Links

- Winbond DDR2 SDRAM 128 MB Surface, 84-Pin 16 bit TFBGA

- Winbond W9712G6KB25I DDR2 SDRAM 128 MB Surface, 84-Pin 16 bit TFBGA

- Winbond SDRAM 512 MB Surface, 84-Pin 16 bit VFBGA

- Winbond W9751G6NB25I SDRAM 512 MB Surface, 84-Pin 16 bit VFBGA

- Winbond SDRAM 128 MB Surface, 54-Pin 16 bit TSOP

- Winbond W9812G6KH-6I SDRAM 128 MB Surface, 54-Pin 16 bit TSOP

- Winbond W9725G6KB-25/TRAY 800MHz, 84-Pin WBGA

- Winbond SDRAM 1 GB Surface, 84-Pin 16 bit